1、 posedge clk and negedge rst_n应该写为posedge clk or negedge rst_n

2、posedge clk or nedge rst_n应该写为posedge clk or negedge rst_n

3、

module LED8(

input clk_100M;

input rst_n;

output [0:7] LED

);

应该定义为:

module LED8(

input clk_100M,

input rst_n,

output [0:7] LED

);

将端口定义包括类型定义一起放在module后的括号内的时候,之间用逗号隔开。

4、数组假设abc[0:7],单个元素写成abc[0]而不是abc(0)。

5、100MHz分频成1Hz。计数为1042*1024*100(27'h640_0000)。

6、两种方式定义信号端口

第一种:

module LED8(clk_100M,rst_n,LED);

input clk_100M;

input rst_n;

output [0:7] LED;

reg [0:7] LED;

reg [0:7] choose; //Choose the LED to highlight

reg [0:26] count;

没错误。

第二种:

module LED8(

input clk_100M,

input rst_n,

output [0:7] LED

);

reg [0:7] LED;

reg [0:7] choose; //Choose the LED to highlight

reg [0:26] count;

提示错误:

ISE软件是:ERROR:HDLCompilers:27 - "LED8.v" line 34 Illegal redeclaration of 'LED'

Quartus软件是:Error (10759): Verilog HDL error at LED8.v(34): object LED declared in a list of port declarations cannot be redeclared within the module body。

都是说重复定义LED信号。

所以,采用第二种的时候,不能再将输出端口定义为reg型。另外,代码中使用assign对LED赋值会提示如下错误:

ERROR:HDLCompilers:247 - "LED8.v" line 60 Reference to vector wire 'led' is not a legal reg or variable lvalue

ERROR:HDLCompilers:106 - "LED8.v" line 60 Illegal left hand side of nonblocking assignment

解决办法:必须添加中间变量如 reg [0:7] abc;使用assign LED = abc;对LED赋值。

小结:第一种定义方法,输出变量若使用assign进行赋值就不能定义为reg型,且需要使用中间变量;若在always中进行赋值就需要定义为reg型;

第二种方法,默认的是wire型,故不能在always中赋值,必须由中间变量用assign赋值。

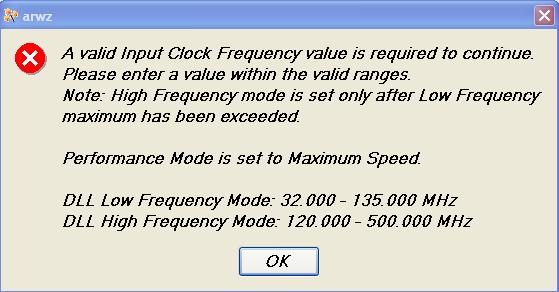

7、本来写了个testbench,才发现要想实现LED变化一次,count要计数1042*1024*100(27'h640_0000)。这么大数据很难看到现象。因为板子的输入时钟就是100M,于是就想通过DCM得到低于10M的数据吧。跳出如下对话框:

即,最小的输出频率是32M。这跟不分频没多大区别了。好吧,我承认,这么高级的板子做跑马灯有些大材小用了。╮(╯▽╰)╭

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。