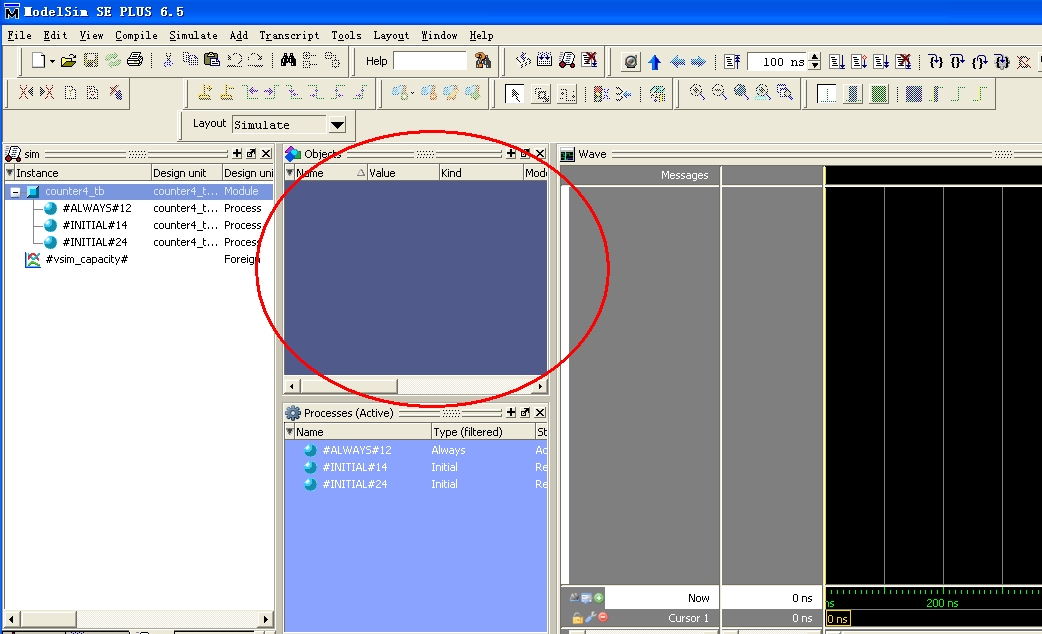

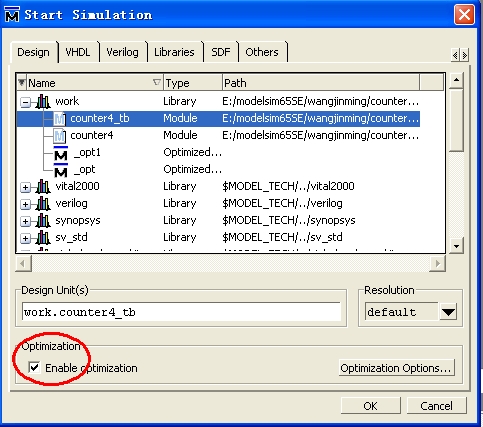

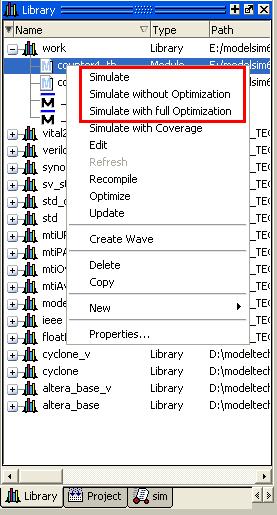

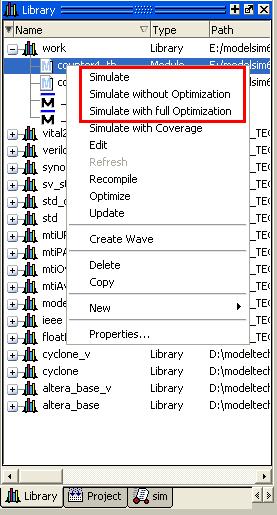

改正方法:去点红圈处的钩。或者如下图,右击要仿真的文件,选中Simulaiton without Optimization.

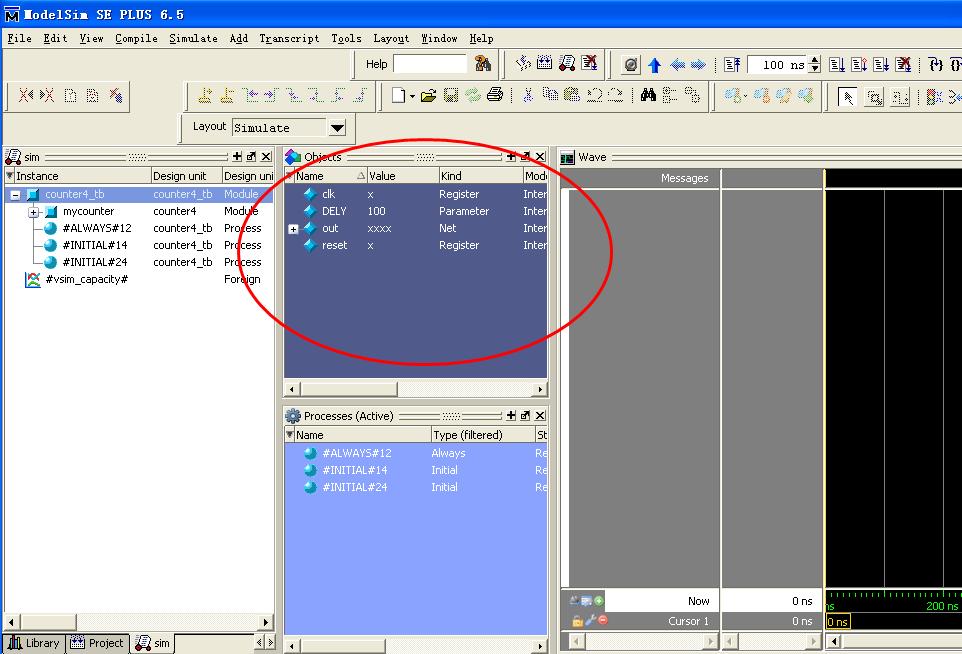

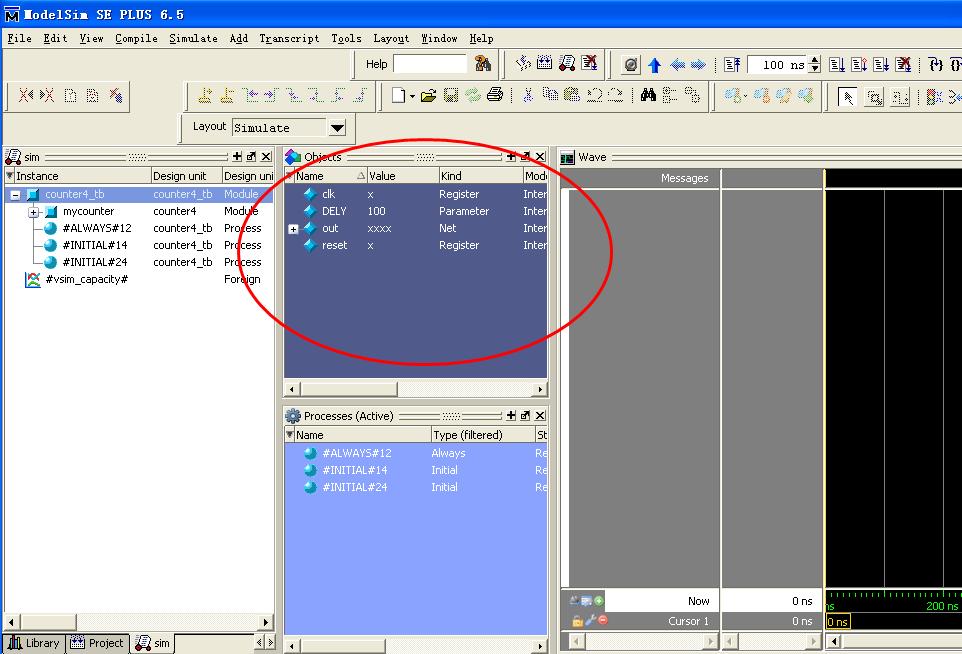

改正之后,Objects中出现了信号:

2011.7.4

4、

发现了

initial

$monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);

的作用,仿真运行后,在Transcript中显示:

0 clk=0 reset=0 out= x

# 50 clk=1 reset=0 out= x

# 100 clk=0 reset=1 out= x

# 150 clk=1 reset=1 out= 0

# 200 clk=0 reset=0 out= 0

# 250 clk=1 reset=0 out= 1

# 300 clk=0 reset=0 out= 1

# 350 clk=1 reset=0 out= 2

# 400 clk=0 reset=0 out= 2

# 450 clk=1 reset=0 out= 3

# 500 clk=0 reset=0 out= 3

5、

在做好一个工程后,想要对另一个文件夹内的文件进行仿真,必须选择Change Directory。可是,选项是暗色的,不能选。我只有关掉modelsim,再打开,才可以选。后来发现,之所以之前不能选是因为还在仿真。只要关掉仿真就可以了。做法如下:选中Simulate->End Simulation。

6、

常用指令总结:

vlib work

vmap work work

vlog xxx.v

vcom xxx.vhd

add wave /name/ *

vsim xxxx

run xxx ns

quit –f

7、

语法错误parameter delay 10; 错因:忘记 = 改为:parameter delay = 10;

语法错误

AOI oi(.A(A),B(B),.C(C),D(D),.F(F));

错因:忘记 .

改为 AOI oi(.A(A),.B(B),.C(C),.D(D),.F(F));

8、

做AOI.v,编译后出现错误

** Error: E:/modelsim65SE/wangjinming/AOI/AOI_tb.v(13): (vlog-2110) Illegal reference to net "A".

错因:原来以为是A = 0; B = 0; C = 0; D = 0;两边没加begin end,加上后编译仍有此错误。后来才发现测试文件的信号定义错误。

源文件端口定义是:

input A,B,C,D;

output F;

测试文件的信号定义应该是:

reg A,B,C,D;

wire F;

即:源文件的输入端在测试文件中定义为reg,源文件的输出端在测试文件中定义为wire.

9、

仿真mux4_1时,我用指令vsim mux4_1_tb,现象objects中没有信号,即没有去掉Enable Optimization。不知道怎么用命令进行不加Enable Optimization的操作,暂时还用鼠标点击选项吧。

10、

对一个语法的理解

之前我使用的时间单位和时间精度为:`timescale 1ns/1ns,在modelsim的横坐标是每一小格为1ns。2011.7.5发现这个结论不对。目前还不能确定仿真时如何设置每小格的大小的。有待进一步研究。2011.7.8发现,时间单位没有确定仿真的每小格的单位,之所以每小格会显示不同的大小,是因为仿真图放大缩小的缘故。

11、

测试模块中的时钟语句:always #delay clk = ~clk;

初始化中必须有clk = 1 或者 clk = 0;否则,仿真时clk无变化。

12、

测试文件中调用源文件模块,则测试文件开头必须用`include “file.v”包含

2011.7.5

13、

警告:

Warning: (vsim-3009) [TSCALE] - Module 'decode4_7' does not have a `timescale directive in effect, but previous modules do.

原因:在测试文件中有:`timescale 。。。,而在源文件中没有

解决方法:在源文件中加入`timescale。。。。如果是`timescale 1ns/1ns,则都可忽略,软件会默认。

14、

做【例5.13】用casez 描述的数据选择器时出现问题。

代码如下:

module mux_casez(out,a,b,c,d,select);

output out;

input a,b,c,d;

input [3:0] select;

reg out;

always @(select or a or b or c or d)

begin

casez(select)

4'b???1 : out = a;

4'b??1? : out = b;

4'b?1?? : out = c;

4'b1??? : out = d;

endcase

end

endmodule

`include "mux_casez.v"

module mux_casez_tb;

wire out;

reg a,b,c,d;

reg [3:0] select;

initial

begin

a = 1; b = 0; c = 1;d = 0;

#20 select = 4'b???1;

#20 select = 4'b??1?;

#20 select = 4'b?1??;

#20 select = 4'b1???;

#20 $stop;

end

mux_casez mux_casez(.out(out),.a(a),.b(b),.c(c),.d(d),.select(select));

endmodule

仿真结果怎么会是这样的呢?

out应该先后电平是1 0 1 0的啊?为什么一直是1

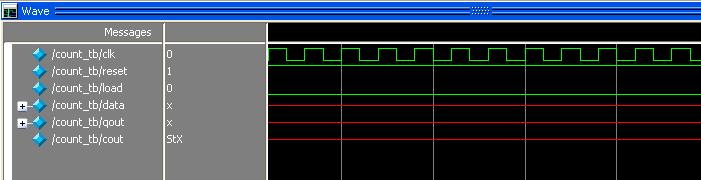

刚开始有人说把casez改成case。这样虽然仿真正确,如下图:

但这就违背了这个例程的要求。后经人指点,将测试文件的?都改为0。仿真也是对的。甚至将测试文件中的?改为等价的z,仿真也是没有现象。

2011.7.6

15、

调用另一个文件时,要使用`include。如果写在一个文件内,则被调用模块要写在调用模块之前。

16、

如果用连续赋值语句assign,则被赋值变量不能定义reg。如下是错误的,需要去掉reg cout;。

assign cout = (qout == 4'hf) ? 1 : 0;

17、

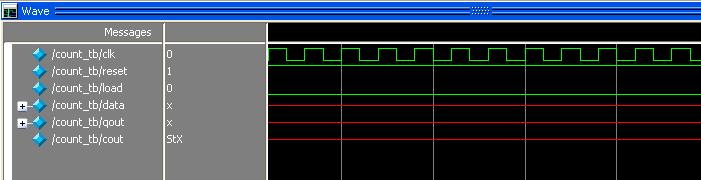

测试文件中初始化initial开始要把所有的输入初始化。,否则可能仿真时一直是未知状态。

错误原因就是在初始化代码中忽略了data = 0;

18、

【例6.8】顺序执行模块1【例6.9】顺序执行模块2两个模块不会仿真。

2011.7.8

19、

在做第八章【例8.20】2 选1 多路选择器的仿真的时候,得到的结果不正确,与书上的不同。

2011.7.9

20、

不太熟悉`define的用法。

21、

下午在做【例9.27】4 位串并转换器,编写好测试文件,打开modelsim,建工程,编译通过,正要仿真,发现找不到测试文件。重新建立工程后出现,吓我一跳,还以为软件坏了。

后来发现另一个问题,这个代码没看懂,加了注释,如下:

module serial_pal(clk,reset,en,in,out);

input clk,reset,en,in;

output [3:0] out;

reg [3:0] out;

always @(posedge clk)

begin

if(reset)

out <= 4'h0;

else if(en)

out <= {out,in}; //不懂

end

endmodule

编译时出现错误:

** Error: E:/modelsim65SE/wangjinming/nine_chapter/serial_pal/serial_pal.v(1): near "EOF": syntax error, unexpected "end of source code"

去掉这个注释后,编译通过。明明被注释了,不知为何还是出错。这个串并转换有缺陷,应该每四位输出一次的。估计是软件发神经了。

22、

Verilog区分大小写的

2011.7.21

23、

做后仿真时,将源文件、测试文件和Quartus编译生成的.vo文件一起编译,仿真时选中测试文件后记得加入仿真库及在SDF下加入Quartus编译生成的sdo文件。

附上王金明《Verilog 程序设计教程》及书中代码。

王金明Verilog HDL程序设计教程.pdf

王金明:《Verilog_HDL_程序设计教程》书中所有代码.doc

2011.9.17

关于这ModelSim SE后仿真的资料许多,但是大部分描述不完整或者主次不分,给初学者带来麻烦。在此,附上我初学时参考的基于Quartus II + ModelSim SE的后仿真教程。我觉得有针对性且容易学会。

基于Quartus II + ModelSim SE的后仿真.zip

2012.5.6

换了自己的笔记本,重新安装modelsim 6.5SE并破解。按照《基于Quartus II + ModelSim SE的后仿真(Verilog版)》中的步骤添加altera仿真库,执行完第二步即新建好文件夹altera_base_v后,要编译仿真库,可是菜单栏中的compile是灰色的,无法选中。我原来以为是没有破解好。几经周折,偶然发现关闭工程后,才能选择主菜单中的compile。

2012.5.9

测试文件引用原文件的路径用/,而不是\