系统:windows XP

软件:Quartus II 9.0;Nios II 9.0

硬件:杭州康芯GW48_PK4++_2C35实验箱

1、 视频同步发生器核(Video Sync Generator Core)和像素转换器核(Pixel Converter Core)(来自:Quartus II Handbook Version 9.0 Volume 5:Embedded Peripherals)

视频同步发生器接收RGB格式的像素数据流,以合适的时序输出到片外显示器。可以配置该核以支持不同的显示器分辨率和同步时序。

像素转换器可以根据视频同步发生器要求的格式传输像素数据。

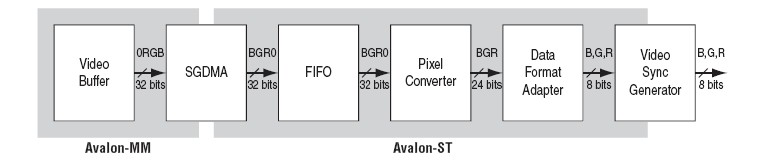

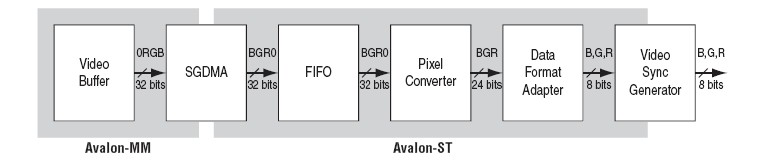

图1 是视频同步发生器和像素转换器的一个连接方式。

图 1 连接方式

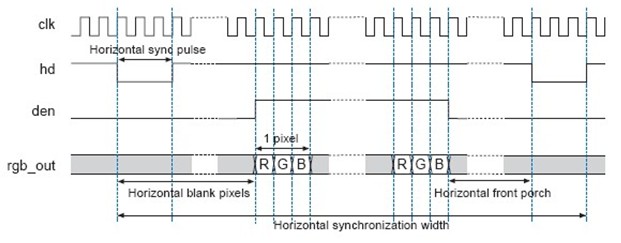

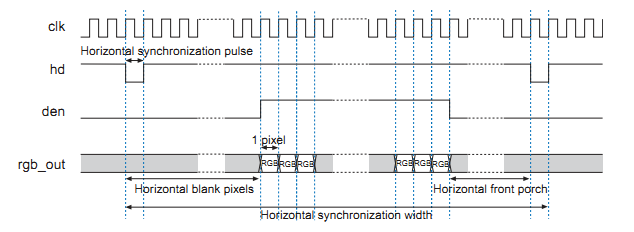

视频同步发生器的行场同步时序有两种配置方式。

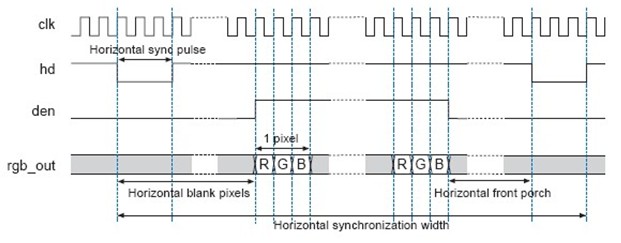

图 2 8 bits数据宽度,发送三次每像素

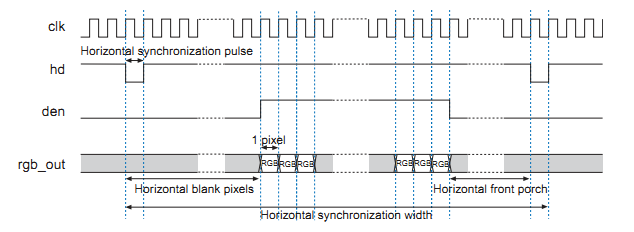

图 3 24 bits数据宽度,发送一次每像素

2、硬件设计

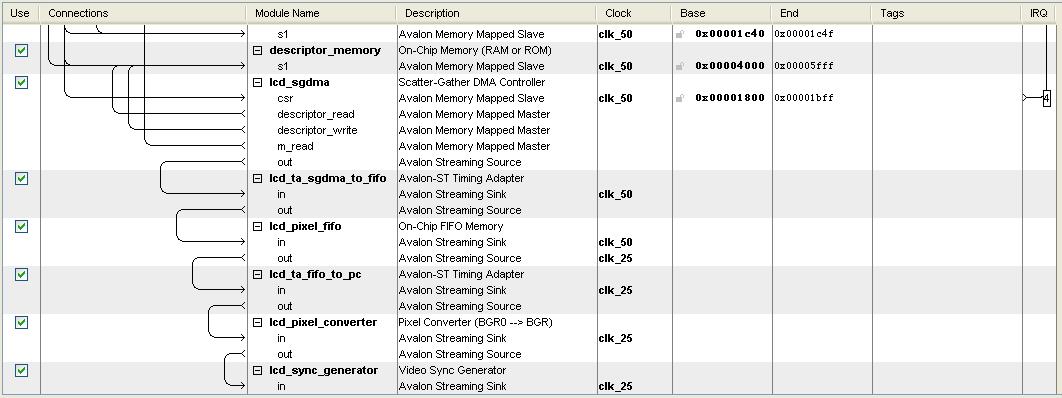

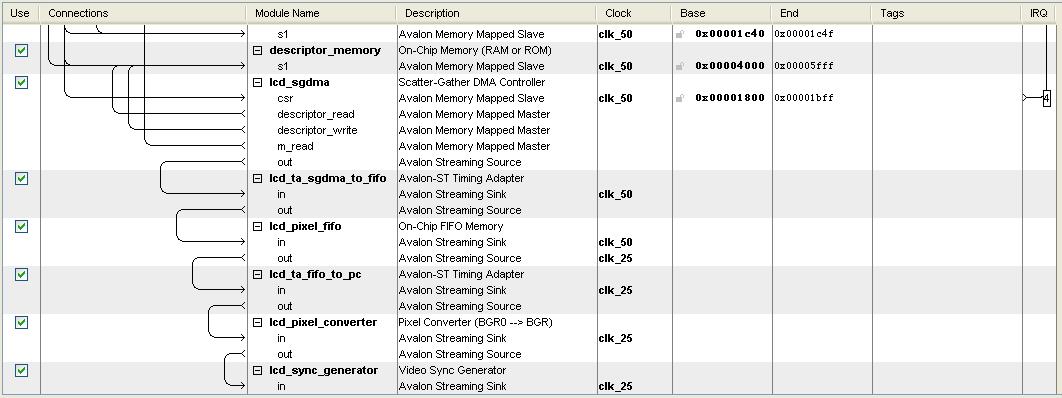

在SOPC中连线如图4所示。

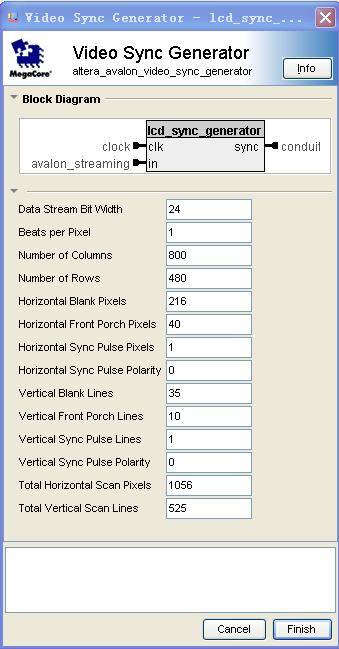

图 4视频同步发生器核和像素转换器核配置

Descriptor_memory可以是sdram。

配置过程:

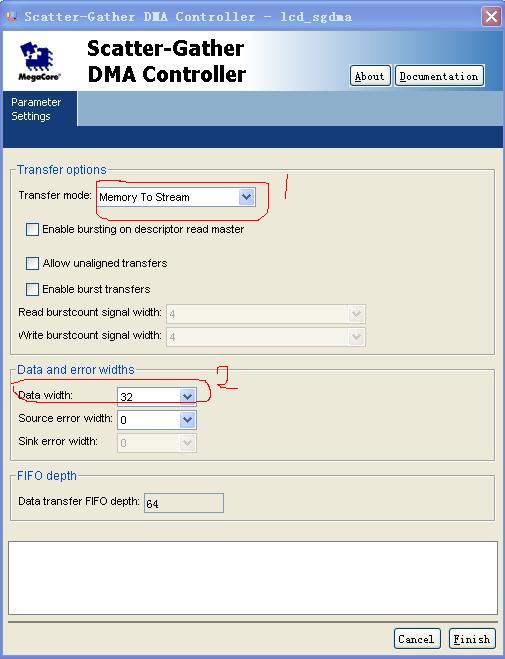

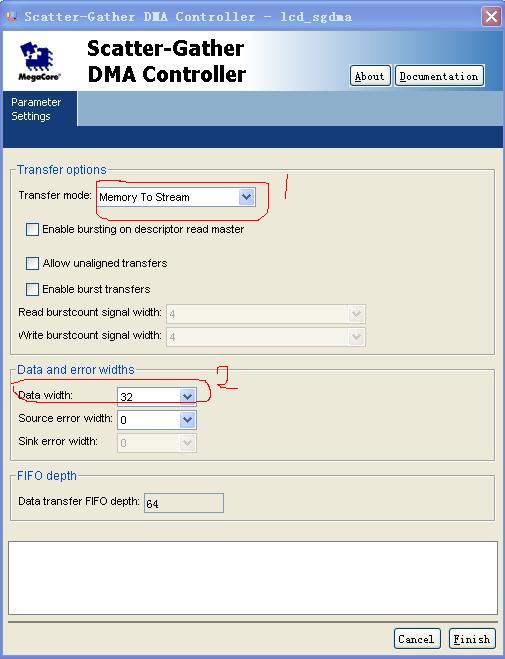

(1)lcd_sgdma

调用IP核:Scatter-Gather DMA Controller

数据流模式为:Memory to stream,数据宽度:32

(2) lcd_ta_sgdma_to_fifo

调用IP核:Avalon-ST Timing Adapter

与FIFO相连的输出接口的Ready Latency 为1;

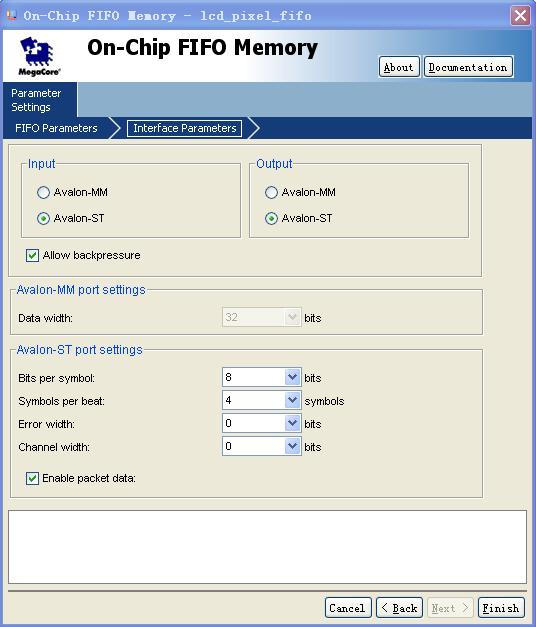

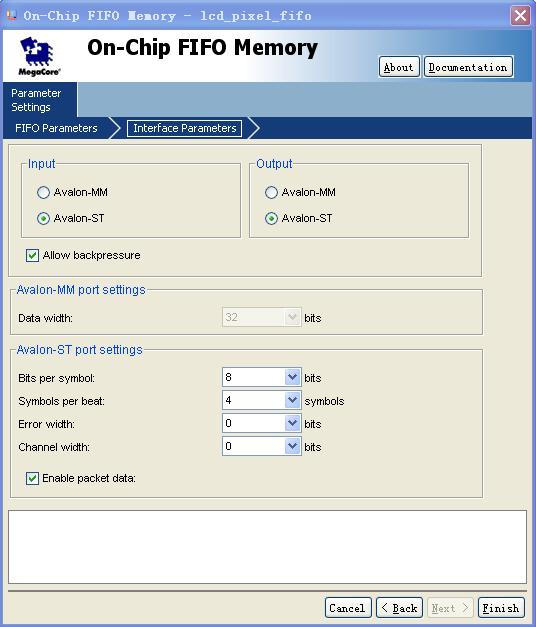

(3) lcd_pixel_fifo

调用IP核:On-Chip FIFO Memory

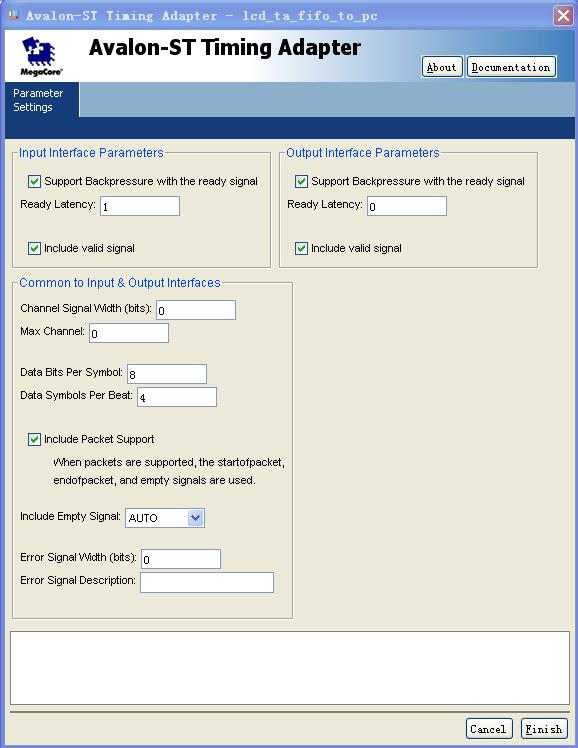

(4) lcd_ta_fifo_to_pc

调用IP核:Avalon-ST Timing Adapter

与FIFO相连的接口的Ready latency 为1

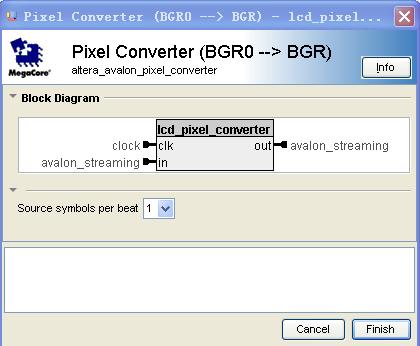

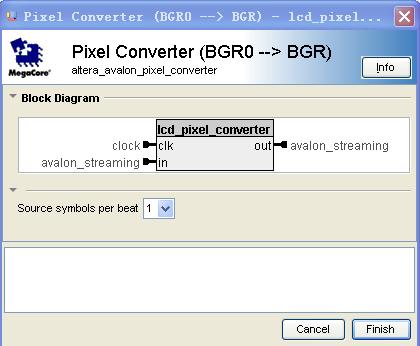

(5) lcd_pixel_converter

调用IP核:Pixel Converter(BGR0-->BGR)

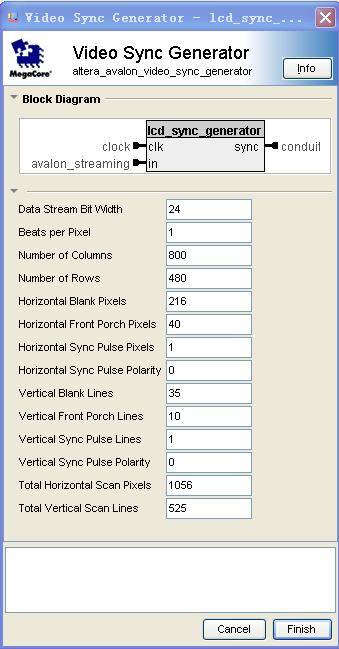

(6) lcd_sync_genetor

调用IP核:Video Sync Generator

选择24bits,发送一次每像素的模式。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。