ISE 约束文件的基本操作

1.约束文件的概念

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管

脚约束以及区域约束。3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF

文件。本节主要介绍UCF文件的使用方法。

UCF文件是ASC

2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。NCF约束文件的语法和UCF文件相同,二者的区别在于:

UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。PCF文件可以分为两个部分:

一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。一般情况下,用户约束都应在UCF文件中完成,不建议直接修改

NCF文件和PCF文件。

2.创建约束文件

约束文件的后缀是.ucf,所以一般也被称为UCF文件。创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取“Implementation Constrains File”,在“File

Name”中输入“one2two_ucf”。单击“Next”按键进入模块选择对话框,选择模块“one2two”,然后单击“Next”进入下一页,

再单击“Finish”按键完成约束文件的创建。

第二种方法:在工程管理区中,将“Source for”设置为“Synthesis/Implementation”。“Constrains

Editor”是一个专用的约束文件编辑器,双击过程管理区中“User Constrains”下的“Create Timing

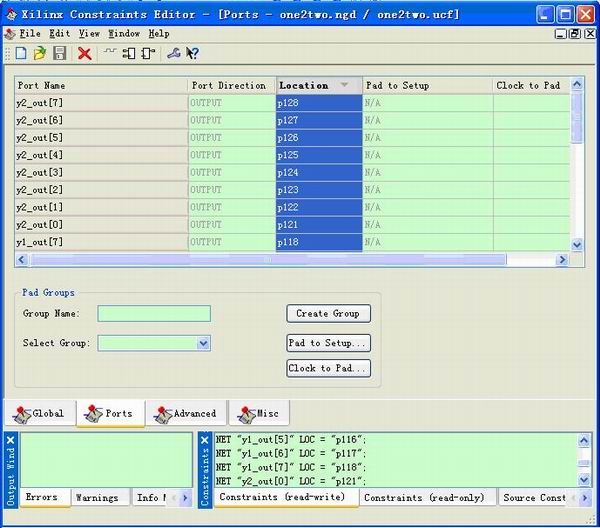

Constrains”就可以打开“Constrains Editor”,其界面如图所示:

图 启动Constrains Editor引脚约束编辑

在“Ports”选项卡中可以看到,所有的端口都已经罗列出来了,如果要修改端口和FPGA管脚的对应关系,只需要在每个端口的“Location”列中填入管脚的编号即可。例如在UCF文件中描述管脚分配的语法为:

NET “端口名称” LOC = 引脚编号;

需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。但是关键字NET是不区分大小写的。

3.编辑约束文件

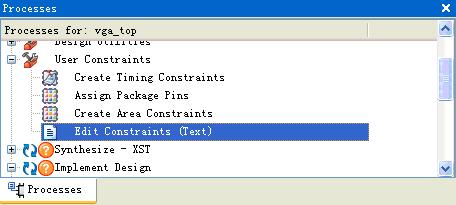

在工程管理区中,将“Source for”设置为“Synthesis/Implementation”,然后双击过程管理区中“User

Constrains”下的“Edit Constraints

(Text)”就可以打开约束文件编辑器,如下图所示,就会新建当前工程的约束文件。

图 用户约束管理窗口

UCF文件的语法说明

1.语法

UCF文件的语法为:

{NET|INST|PIN} "signal_name" Attribute;

其中,“signal_name”是指所约束对象的名字,包含了对象所在层次的描述;“Attribute”为约束的具体描述;语句必须以分号“;”结

束。可以用“#”或“/*

*/”添加注释。需要注意的是:UCF文件是大小写敏感的,信号名必须和设计中保持大小写一致,但约束的关键字可以是大写、小写甚至大小写混合。例如:

NET "CLK" LOC = P30;

“CLK”就是所约束信号名,LOC = P30;是约束具体的含义,将CLK信号分配到FPGA的P30管脚上。

对于所有的约束文件,使用与约束关键字或设计环境保留字相同的信号名会产生错误信息,除非将其用" "括起来,因此在输入约束文件时,最好用" "将所有的信号名括起来。

2.通配符

在UCF文件中,通配符指的是“*”和“?”。“*”可以代表任何字符串以及空,“?”则代表一个字符。在编辑约束文件时,使用通配符可以快速选择一组信号,当然这些信号都要包含部分共有的字符串。例如:

NET "*CLK?" FAST;

将包含“CLK”字符并以一个字符结尾的所有信号,并提高了其速率。

在位置约束中,可以在行号和列号中使用通配符。例如:

INST "/CLK_logic/*" LOC = CLB_r*c7;

把CLK_logic层次中所有的实例放在第7列的CLB中。

3.定义设计层次

在UCF文件中,通过通配符*可以指定信号的设计层次。其语法规则为:

* 遍历所有层次

Level1/* 遍历level1及以下层次中的模块

Level1/*/ 遍历level1种的模块,但不遍历更低层的模块

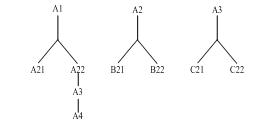

例4-5 根据图4-75所示的结构,使用通配符遍历表4-3所要求的各个模块。

图 层次模块示意图

表 要求遍历的符号列表

管脚和区域约束语法

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。此外,

LOC还能将一组基本单元约束在特定区域之中。LOC语句既可以书写在约束文件中,也可以直接添加到设计文件中。换句话说,ISE中的FPGA底层工具编

辑器(FPGA Editor)、布局规划器(Floorplanner)和引脚和区域约束编辑器的主要功能都可以通过LOC语句完成。

INST "instance_name " LOC = location;

其中“location”可以是FPGA芯片中任一或多个合法位置。如果为多个定位,需要用逗号“,”隔开,如下所示:

LOC = location1,location2,...,locationx;

目前,还不支持将多个逻辑置于同一位置以及将多个逻辑至于多个位置上。需要说明的是,多位置约束并不是将设计定位到所有的位置上,而是在布局布线过程中,布局器任意挑选其中的一个作为最终的布局位置。

范围定位的语法为:

INST “instance_name” LOC=location:location [SOFT];

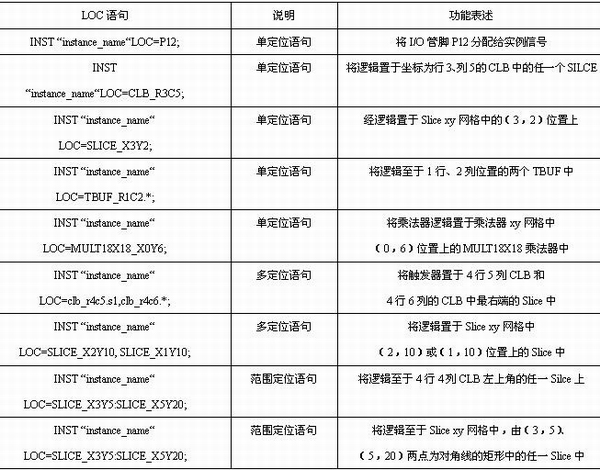

常用的LOC定位语句如表4-4所列。

表 常用的LOC定位语句

使用LOC完成端口定义时,其语法如下:

NET "Top_Module_PORT" LOC = "Chip_Port";

其中,“Top_Module_PORT”为用户设计中顶层模块的信号端口,“Chip_Port”为FPGA芯片的管脚名。

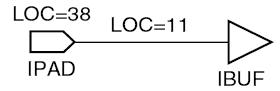

LOC语句中是存在优先级的,当同时指定LOC端口和其端口连线时,对其连线约束的优先级是最高的。例如,在图4-76中,LOC=11的优先级高于LOC=38。

图 LOC优先级示意图

2.LOC属性说明

LOC语句通过加载不同的属性可以约束管脚位置、CLB、Slice、TBUF、块RAM、硬核乘法器、全局时钟、数字锁相环(DLL)以及DCM模块等

资源,基本涵盖了FPGA芯片中所有类型的资源。由此可见,LOC语句功能十分强大,表4-5列出了LOC的常用属性。

表 LOC语句常用属性列表

转自:http://bbs.****.com/BLOG_ARTICLE_144140.HTM

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。